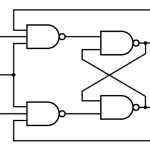

Gated SR latch

In some situations it may be desirable to dictate when the latch can and cannot latch. The gated SR latch is a simple extension of the SR latch which provides an Enable line which must be driven high before data can be latched. Even though a control line is now required, the SR latch is not synchronous, because the inputs can change the output even in the middle of an enable pulse.

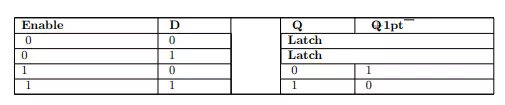

When the Enable input is low, then the outputs from the AND gates must also be low, thus the Q and Q 1pt outputs remain latched to the previous data. Only when the enable input is high can the state of the latch change, as shown in the truth table. When the enable line is asserted, a gated SR latch is identical in operation to an SR latch.

The Enable line is sometimes a clock signal, but is usually a read or write strobe.

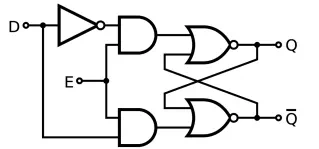

Gated D latch

The D latch (D for ”data”) or transparent latch is a simple extension of the gated SR latch that removes the possibility of invalid input states.

Since the gated SR latch allows us to latch the output without using the S or R inputs, we can remove one of the inputs by driving both the Set and Reset inputs with a complementary driver: we remove one input and automatically make it the inverse of the remaining input.

The D latch outputs the D input whenever the Enable line is high, otherwise the output is whatever the D input was when the Enable input was last high. This is why it is also known as a transparent latch – when Enable is asserted, the latch is said to be ”transparent” – it signals propagate directly through it as if it isn’t there.

D latches are often used in I/O ports of integrated circuits and are available as discrete devices, often multiply packaged. An example is the 74HC75, part of the 7400 series of ICs, containing four separate D latches.