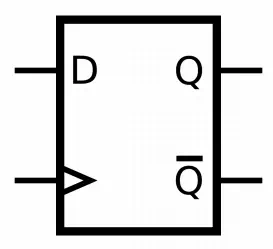

D flip-flop

The D flip-flop is the edge-triggered variant of the transparent latch. On the rising (usually, although negative edge triggering is just as possible) edge of the clock, the output is given the value of the D input at that moment . The output can only change at the clock edge, and if the input changes at other times, the output will be unaffected.

D flip-flops are by far the most common type of flip-flops and some devices (for example some FPGAs) are made entirely from D flip-flops. They are also commonly used for shift registers and input synchronisation.

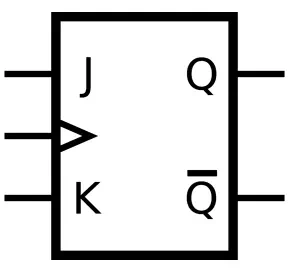

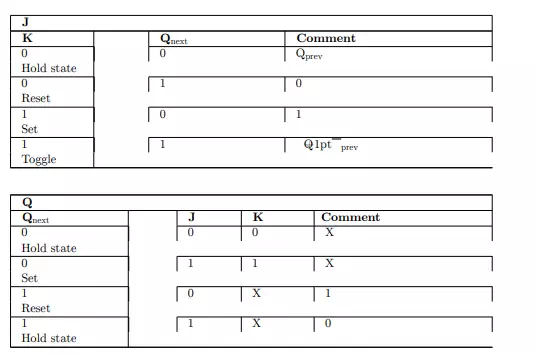

JK Flip-flop

The JK flip-flop is a simple enhancement of the SR flip-flop where the state J=K=1 is not forbidden. It works just like a SR FF where J is serving as set input and K serving as reset. The only difference is that for the formerly “forbidden” combination J=K=1 this flip-flop now performs an action: it inverts its state. As the behaviour of the JK flip-flop is completely predictable under all conditions, this is the preferred type of flip-flop for most logic circuit designs. But there is still a problem i.e. both the outputs are same when one tests the circuit practically. This is because of the internal toggling on every propagation elapse completion. The main remedy is going for master-slave jk flip-flop, this ff overrides the self(internal) recurring toggling through the pulsed clocking feature incorporated.

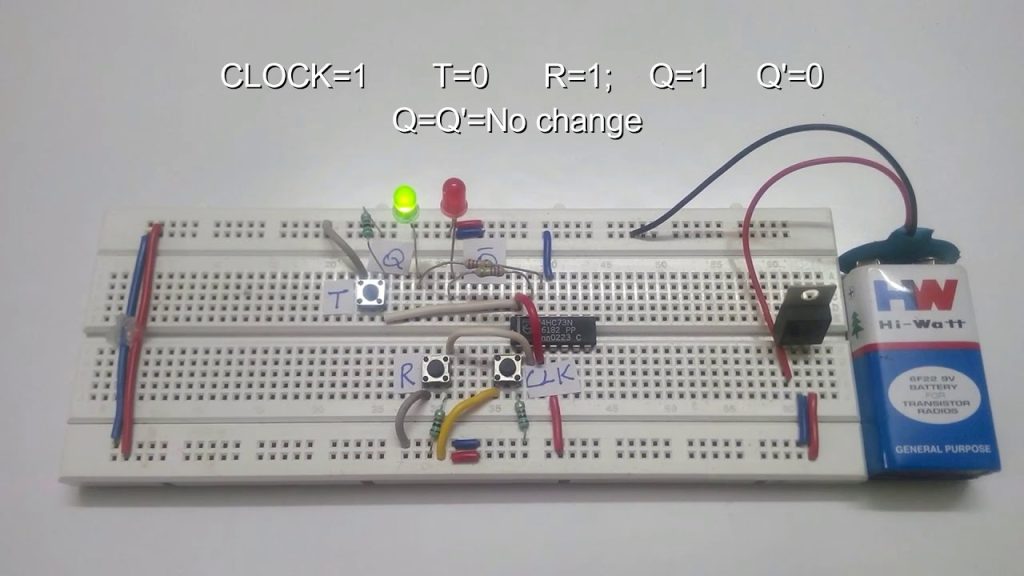

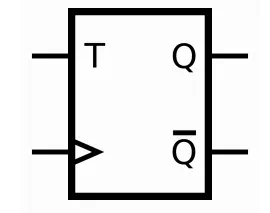

T flip-flops

A T flip-flop is a device which swaps or ”toggles” state every time it is triggered if the T input is asserted, otherwise it holds the current output. This behaviour is described by the characteristic equation:

and can be described either of the following tables:

A circuit symbol for a T-type flip-flop: T is the toggle input and Q is the stored data output.